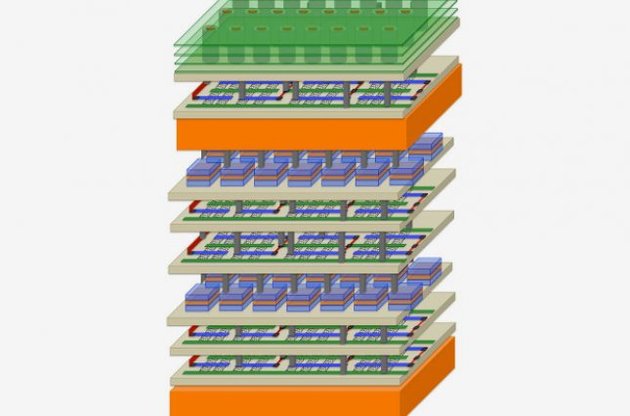

Вчені зі Стенфордського університету розробили комп'ютерний чіп N3XT (Nano-Engineered Computing Systems Technology) з "багатоповерховою" архітектурою, в якій процесорні шари чергуються з шарами пам'яті. Як вважають розробники, дана архітектура дозволить зробити нові чіпи більш продуктивними і менш енергоспоживаючими.

У N3XT процесори та пам'ять з'єднані мільйонами коротких електропровідних доріжок, які забезпечують обмін сигналами між усіма компонентами. За словами одного з розробників N3XT, при порівнянному з звичайними чіпами кількості обчислювальних одиниць і обсягу пам'яті новий "багатоповерховий" чіп буде перевершувати по продуктивності старий в тисячу разів. У N3XT замість звичайних кремнієвих транзисторів використовуються транзистори з вуглецевих нанотрубок.

Пам'ять для нового чіпа створюється за традиційно кремнієвої технології. Однак подробиці виробництва нового чіпа не розкриваються. Відомо тільки, що всі шари N3XT спочатку створюються окремо, а потім вже розміщуються один над одним і електрично з'єднуються. Для зниження температури працюючого багатошарового чіпа науковці інтегрували в кожен шар спеціальний теплопровідний матеріал.

У липні компанія IBM розробила 3, доступні на ринку.

Увійти за допомогою Google

Увійти за допомогою Google